青少年不可不知的大數據、網絡與信息安全軟件開發新趨勢

在數字化浪潮席卷全球的今天,青少年不僅是網絡的原住民,更是未來科技創新的主力軍。大數據、網絡與信息安全已成為影響社會發展的重要領域,而相關的軟件開發技能,正逐漸成為青少年面向未來不得不了解的核心知識。這不僅關乎個人發展,更與國家數字安全與創新能力緊密相連。

一、大數據:透視世界的“新顯微鏡”

大數據已滲透到生活的方方面面。從社交媒體的個性化推薦,到智慧城市的交通管理,再到學習平臺的精準分析,數據無處不在。對青少年而言,理解大數據意味著:

- 數據思維培養:學會從海量信息中識別模式、發現問題,這是未來決策的基礎。

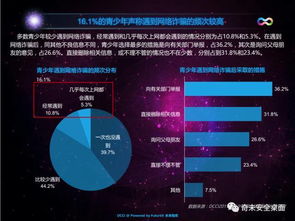

- 隱私保護意識:明白個人數據如何被收集、使用,建立負責任的數據分享觀念。

- 職業新機遇:數據分析師、算法工程師等新興職業,正成為高需求崗位。

二、網絡:連接萬物的“數字橋梁”

5G、物聯網等技術的普及,讓網絡連接更加緊密。青少年需要了解:

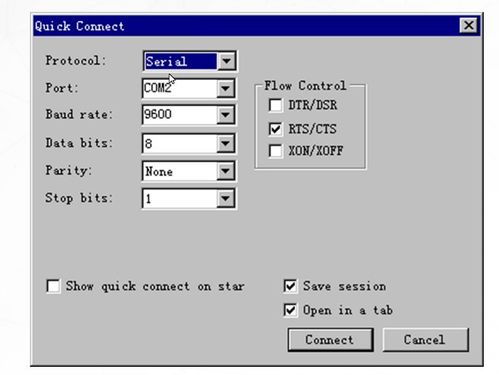

1. 網絡基礎設施:從基礎協議到云計算,理解網絡如何運作。

2. 網絡倫理與法規:明確網絡行為的邊界,抵制網絡暴力、虛假信息。

3. 開發實踐:學習網頁開發、移動應用設計,將創意轉化為現實。

三、信息安全:數字時代的“守護盾牌”

隨著網絡攻擊事件頻發,信息安全的重要性日益凸顯。青少年應掌握:

- 常見威脅認知:了解病毒、釣魚攻擊、數據泄露等風險。

- 防護技能基礎:學習密碼管理、加密技術、安全軟件使用。

- 軟件開發中的安全實踐:在編程中融入安全設計,如輸入驗證、漏洞防范。

四、軟件開發:賦能創新的“核心引擎”

掌握軟件開發能力,能讓青少年從技術使用者轉變為創造者。重點方向包括:

- 編程語言入門:Python、JavaScript等語言易學且應用廣泛。

- 開源工具與平臺:利用GitHub等社區參與項目,提升協作能力。

- 融合性項目實踐:開發結合大數據分析的安全應用,如隱私保護工具、網絡行為監測軟件。

五、行動建議:從認知到實踐

- 學校教育結合:鼓勵學校開設相關課程,融入信息技術教育。

- 家庭引導支持:家長可提供資源,如在線課程、編程工具,并共同討論網絡案例。

- 社會資源利用:參與科技競賽、夏令營,接觸行業專家,拓寬視野。

大數據、網絡與信息安全不僅是技術概念,更是現代公民素養的一部分。青少年盡早了解這些領域,不僅能提升自身競爭力,還能為構建安全、創新的數字未來貢獻力量。從今天開始,擁抱技術、學習開發、守護安全,讓數字世界因年輕一代而更加美好。

如若轉載,請注明出處:http://www.lllji.cn/product/48.html

更新時間:2026-02-21 13:11:03